Hello Jared.

Now I am starting to use SUNXI_CCU_FRACTIONAL for PLL_VIDEO register.

SUNXI_CCU_FRACTIONAL(F1C100S_CLK_PLL_VIDEO, "pll_video", "osc24m",

PLL3_CFG_REG, /* reg */

__BITS(14,8), /* m */

1, /* m_min */

128, /* m_max */

__BIT(24), /* div_en */

__BIT(25), /* frac_sel */

270000000, 297000000, /* frac values */

__BITS(3,0), /* prediv */

0, /* prediv_val */

__BIT(31), /* enable */

SUNXI_CCU_FRACTIONAL_SET_ENABLE),

PLL3_CFG_REG, /* reg */

__BITS(14,8), /* m */

1, /* m_min */

128, /* m_max */

__BIT(24), /* div_en */

__BIT(25), /* frac_sel */

270000000, 297000000, /* frac values */

__BITS(3,0), /* prediv */

0, /* prediv_val */

__BIT(31), /* enable */

SUNXI_CCU_FRACTIONAL_SET_ENABLE),

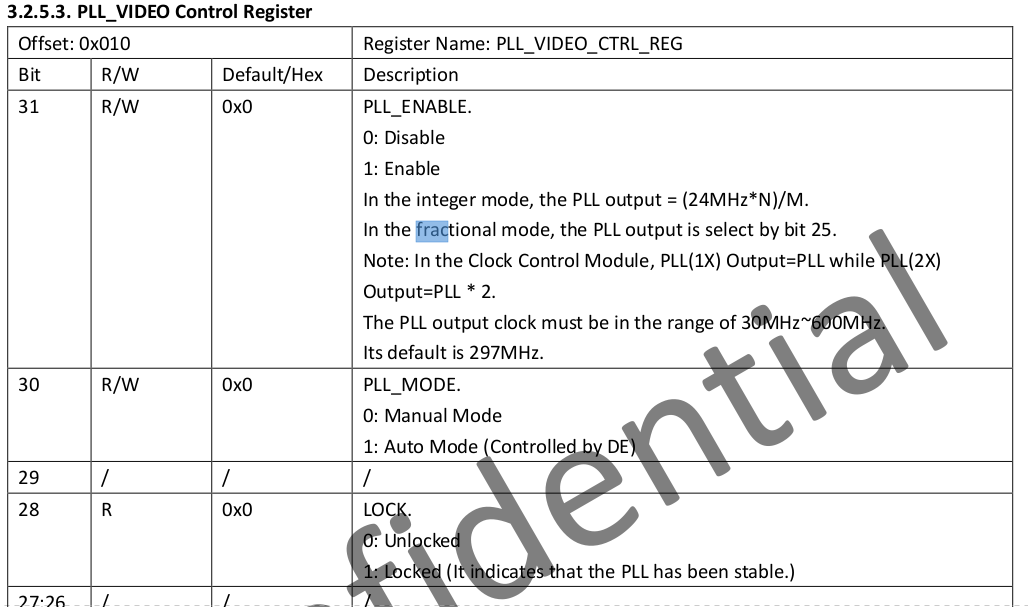

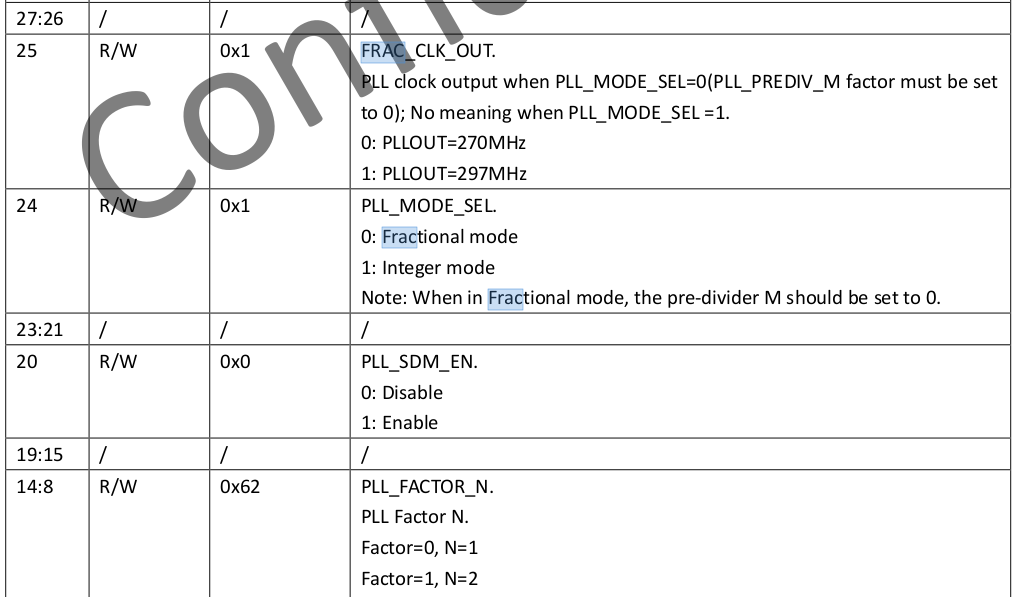

According to the chip description the final clock out PLL_VIDEO is

1. integer mode:

- In the integer mode, the PLL output = (24MHz*N)/M.

accordint to sunxi_ccu_fractional_get_rate() in sunxi_ccu_fractional.c:

the **m** fileld: __BITS(14,8) represents PLL_FACTOR_N

the **prediv** field: __BITS(3,0) represents PLL_PREDIV_M

2. fractional mode:

- 270000000, 297000000

and I have read the referring code in sun4i_a10_ccu.c, there is something miss matched.

SUNXI_CCU_FRACTIONAL(A10_CLK_PLL_VIDEO1, "pll_video1", "osc24m",

PLL7_CFG_REG, /* reg */

__BITS(7,0), /* m */

9, /* m_min */

127, /* m_max */

__BIT(15), /* div_en */

__BIT(14), /* frac_sel */

270000000, 297000000, /* frac values */

0, /* prediv */

8, /* prediv_val */

__BIT(31), /* enable */

0),

PLL7_CFG_REG, /* reg */

__BITS(7,0), /* m */

9, /* m_min */

127, /* m_max */

__BIT(15), /* div_en */

__BIT(14), /* frac_sel */

270000000, 297000000, /* frac values */

0, /* prediv */

8, /* prediv_val */

__BIT(31), /* enable */

0),

int the previous code, the **m** filed represents PLL3_FACTOR_M.

so here for SUNXI_CCU_FRACTIONAL, **m** fields should be maped to **factor** of the register?

and the **prediv** field should be maped to **prediv** of the register?

Best Guards!

-- Han Pengfei (kurain)