Below is the code for ccu array. and I have read from the sun4i-a10-ccu.c that:

1. add the hosc select or enable clock configuration

2. add the next pll clock configuration

so the code is below:

static const char *cpu_parents[] = { "losc", "osc24m", "pll_cpu" };

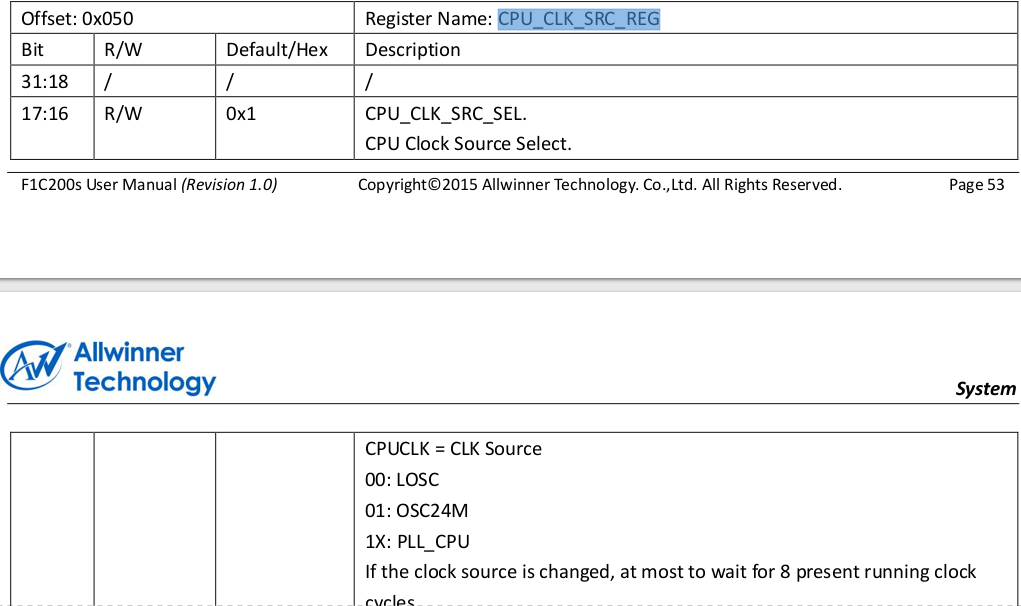

the previous line shows the description for

we have three selects for cpu_clk and the bits is _BITS(17,16), range from losc/osc24M/pll_cpu.

also we don't have any enable/div requires, just 3 selects for this.

static struct sunxi_ccu_clk suniv_f1c100s_ccu_clks[] = {

SUNXI_CCU_DIV(F1C100S_CLK_HOSC, "cpu", cpu_parents,

OSC24M_CFG_REG, /* reg */

0, /* div */

__BITS(17,16), /* sel */

SUNXI_CCU_DIV_SET_RATE_PARENT),

SUNXI_CCU_NKMP_TABLE(F1C100S_CLK_HOSC, "pll_cpu", "osc24m",

PLL1_CFG_REG, /* reg */

__BITS(12,8), /* n */

__BITS(5,4), /* k */

__BITS(1,0), /* m */

__BITS(17,16), /* p */

__BIT(31), /* enable */

__BIT(28), /* lock */

0, /* table */

SUNXI_CCU_NKMP_FACTOR_P_POW2 | SUNXI_CCU_NKMP_FACTOR_N_EXACT |

| SUNXI_CCU_NKMP_SCALE_CLOCK),

for the next NKMP table, it's the description for PLL_CPU, it needs n/k/m/p, enable, and lock operation, as the code.

and there is some requirements:

- for N field, I masked the flag SUNXI_CCU_NKMP_FACTOR_N_EXACT for the below factor:

PLL_FACTOR_N

PLL Factor N.

Factor=0, N=1

Factor=1, N=2

Factor=2, N=3

......

Factor=31,N=32

PLL Factor N.

Factor=0, N=1

Factor=1, N=2

Factor=2, N=3

......

Factor=31,N=32

- for P field, I masked the flag SUNXI_CCU_NKMP_FACTOR_P_POW2 for:

PLL_OUT_EXT_DIV_P

PLL Output External Divider P

00: /1

01: /2

10: /4

PLL Output External Divider P

00: /1

01: /2

10: /4

- for K field, according to sunxi_ccu_nkmp.c, it will auto increase, we do nothing here.

And for the SUNXI_CCU_NKMP_SCALE_CLOCK, I am not sure its final influence.

Best Guards!

-- Han Pengfei (kurain)